- 您现在的位置:买卖IC网 > Sheet目录345 > MT48H8M16LFB4-75 IT:K TR (Micron Technology Inc)IC SDRAM 128MBIT 133MHZ 54VFBGA

128Mb: x16 Mobile SDRAM

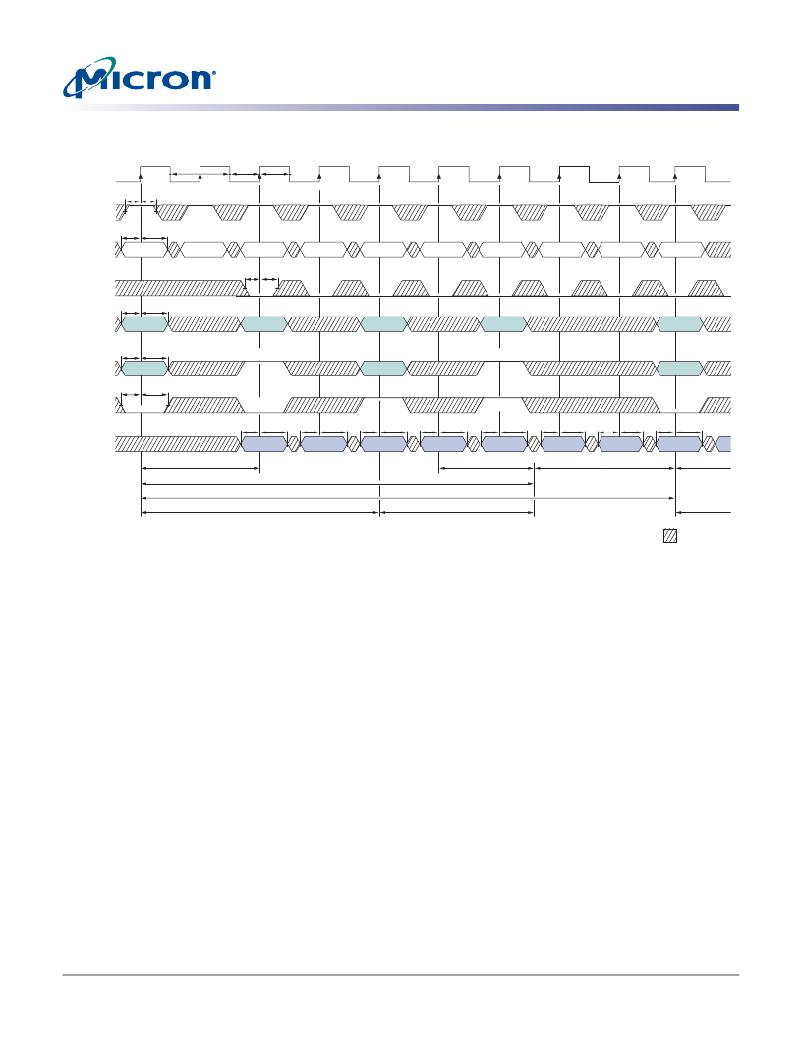

Timing Diagrams

Figure 47:

Alternating Bank Write Accesses

CLK

T0

tCK

T1

tCL

T2

tCH

T3

T4

T5

T6

T7

T8

T9

CKE

tCKS

tCMS

tCKH

tCMH

COMMAND

ACTIVE

NOP

WRITE

NOP

ACTIVE

NOP

WRITE

NOP

NOP

ACTIVE

DQM

tCMS

tCMH

tA S

tAH

A0–A9, A11

A10

ROW

tA S

tAH

ROW

COLUMN m 2

ENABLE AUTO PRECHARGE

ROW

ROW

COLUMN b 2

ENABLE AUTO PRECHARGE

ROW

ROW

tAS

tAH

BA0, BA1

BANK 0

BANK 0

BANK 1

BANK 1

BANK 0

t DS

tDH

t DS

tDH

t DS

tDH

t DS

tDH

t DS

tDH

t DS

tDH

tDS

tDH

t DS

tDH

DQ

D IN m

D IN m + 1

D IN m + 2

D IN m + 3

D IN b

D IN b + 1

D IN b + 2

D IN b + 3

tRCD - BANK 0

tWR - BANK 0

tRP - BANK 0

t RCD - BANK 0

tRAS - BANK 0

t RC - BANK 0

t RRD

Notes:

1. For this example, BL = 4.

2. A9 and A11 are “Don’t Care.”

tRCD - BANK 1

t WR - BANK 1

DON’T CARE

PDF: 09005aef8237e877/Source: 09005aef8237e8d8

128Mb_x16 Mobile SDRAM_Y25M_2.fm - Rev. C 2/07 EN

61

Micron Technology, Inc., reserves the right to change products or specifications without notice.

?2006 Micron Technology, Inc. All rights reserved.

发布紧急采购,3分钟左右您将得到回复。

相关PDF资料

MTC100-JA2-P34

CONTACT INSERT PIN

MX841BE

IC CONVERTER WHITE LED 8-SOIC

MXHV9910BTR

IC LED DRIVER HIGH BRIGHT 8-SOIC

MXN12FB12F

MOTOR BRUSHED DC 12V 2922RPM

MXN13FB08B1

MOTOR BRUSHED DC 8V 4714RPM

N01L63W2AB25I

IC SRAM ASYNC 1MBIT ULP 48-BGA

N01L63W3AB25I

IC SRAM 1MBIT 3V LP 48-BGA

N01L83W2AN5I

IC SRAM 1MB ASYNC CMOS 3STSOP-I

相关代理商/技术参数

MT48H8M16LFB4-8

制造商:Micron Technology Inc 功能描述:IC SDRAM 128MBIT 125MHZ 54VFBGA

MT48H8M16LFB4-8 IT

制造商:Micron Technology Inc 功能描述:IC SDRAM 128MBIT 125MHZ 54VFBGA

MT48H8M16LFB4-8 IT TR

功能描述:IC SDRAM 128MBIT 125MHZ 54VFBGA RoHS:是 类别:集成电路 (IC) >> 存储器 系列:- 标准包装:96 系列:- 格式 - 存储器:闪存 存储器类型:FLASH 存储容量:16M(2M x 8,1M x 16) 速度:70ns 接口:并联 电源电压:2.65 V ~ 3.6 V 工作温度:-40°C ~ 85°C 封装/外壳:48-TFSOP(0.724",18.40mm 宽) 供应商设备封装:48-TSOP 包装:托盘